## Datasheet

# TX6F-SX51D-01 TOSA

## DESCRIPTION

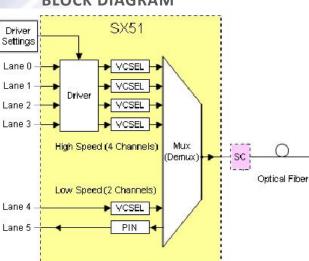

The TX6F-SX51D-01 (TX-SX51) is an optical subassembly (OSA) with bi-direction comm and control link capabilities. The TX-SX51 can transmit up to four videoor data-lanes (up to 3.5Gbps per channel) and one low-speed lane, while simultaneously receiving one low-speed signal, all on *a single* multimode fiber. With the laser driver embedded in the OSA and a ZIF-terminated flex circuit, the TX-SX51 is a bi-directional TOSA also capable of receiving a control signal thereby enabling increased flexibility in system design, extending to applications in DVI and HDMI<sup>™</sup> v1.4.

### **FEATURES**

- Up to 3.5 Gbps on each of the 4 highspeed data channels

- 5 transmit lanes and 1 receive lane over 1 multimode fiber

- HDMI<sup>™</sup> 1.4-capable

- On-board High Speed Laser Driver with individual modulation and bias control of each VCSEL

- Low-stress, highly flexible ZIF connection

- Low power consumption

- High-speed CML inputs

### **APPLICATIONS**

- High-speed Optical Links

- DVI Optical Extenders

- DVI Switches

- HDMI<sup>™</sup> Matrix Switches

- HDMI<sup>™</sup> Optical Extenders

### **ORDERING INFORMATION**

| PART NUMBER    | DESCRIPTION                                                                                                     |

|----------------|-----------------------------------------------------------------------------------------------------------------|

| TX6F-SX51D-01  | 4-ch Transmitter Optical Subassembly,<br>3.5 Gbps per channel plus 5 Mbps Bi-di channel                         |

| TX6F-SX51D-01C | 4-ch Transmitter Optical Subassembly,<br>3.5 Gbps per channel plus 5 Mbps Bi-di channel<br>with Clip            |

| TX6F-SX51D-01H | 4-ch Transmitter Optical Subassembly,<br>3.5 Gbps per channel plus 5 Mbps Bi-di channel<br>with Heatsink & Clip |

### **BLOCK DIAGRAM**

TX6F-SX51D-01 TOSA

### **ABSOLUTE MAXIMUM RATINGS**

| PARAMETER                                              | SYMBOL          | MIN  | MAX | UNITS |

|--------------------------------------------------------|-----------------|------|-----|-------|

| Storage Temperature <sup>1</sup>                       | T <sub>st</sub> | -40  | 85  | °C    |

| Supply Voltage                                         | V <sub>cc</sub> | -0.3 | 3.6 | V     |

| Operating Ceramic (substrate) Temperature <sup>2</sup> | Ta              | 0    | 70  | °C    |

| Operating Humidity <sup>3</sup>                        | RH              |      | 80  | %     |

Notes:

1. Stresses listed may be applied without causing damage. Functionality at or above the values listed is not implied. Exposure to these values for extended periods may affect reliability.

2. See outline drawing for measurement point. Inneos strongly recommends mounting with a heat sink.

3. Non condensing humidity.

### **OPTICAL SPECIFICATIONS – HIGH-SPEED LANES**

| PARAMETER                                      | SYMBOL          | MIN   | ТҮР | MAX | UNITS |

|------------------------------------------------|-----------------|-------|-----|-----|-------|

| Average Optical Power, per Lane <sup>1,2</sup> | Pout            | -3.0  | 0.0 |     | dBm   |

| Optical Modulation Amplitude                   | OMA             | -6.25 |     |     | dBm   |

| Center Wavelength – Lane 0                     | λ <sub>0</sub>  |       | 778 |     | nm    |

| Center Wavelength – Lane 1                     | λ1              |       | 800 |     | nm    |

| Center Wavelength – Lane 2                     | λ <sub>2</sub>  |       | 825 |     | nm    |

| Center Wavelength – Lane 3                     | λ <sub>3</sub>  |       | 850 |     | nm    |

| Optical Rise/Fall Time <sup>3</sup>            | T <sub>tr</sub> |       |     | 100 | Ps    |

Notes:

1. All laser bias and modulations settings are pre-programmed. Users cannot modify these settings.

2. I = 5mA, T=25°C.

3. Rise and fall times measured from 20 –80%. Tested with Inneos reference circuits.

### **ELECTRICAL SPECIFICATIONS – HIGH-SPEED LANES**

| PARAMETER                                    | SYMBOL               | MIN  | ТҮР  | MAX             | UNITS             |

|----------------------------------------------|----------------------|------|------|-----------------|-------------------|

| Data Rate per Lane <sup>1</sup>              | DR                   |      |      | 3.50            | Gb/s              |

| Total Jitter (RMS), per lane <sup>2</sup>    | T <sub>J1</sub>      |      | 10   |                 | ps                |

| Input Differential Impedance                 | Z <sub>DIFF</sub>    |      | 100  |                 | ohm               |

| Differential Input Voltage <sup>3</sup>      | V <sub>IN-DIFF</sub> | 320  |      | 2000            | mV <sub>p-p</sub> |

| Single-ended Input Voltage                   | V <sub>IN-SE</sub>   | 160  |      | 1000            | mV <sub>p-p</sub> |

| Common mode input voltage (AC-coupled input) | V <sub>IN-CM</sub>   | 0.85 | 2.6  | V <sub>CC</sub> | V                 |

| Operating Supply Voltage                     | V <sub>cc</sub>      | 3.15 | 3.30 | 3.45            | V                 |

| Operating Supply Current                     | I <sub>cc</sub>      |      | 140  |                 | mA                |

#### Notes:

1. Requires DC-balanced data pattern. Measured with input signals conforming to HDMI rev 1.3a, Section 4.2.4, Figure 4-18.

2. Based on a jitter-free source

3. Differential CML compatible inputs

## Datasheet

# P1RX6A-SX51x-01 ROSA

## DESCRIPTION

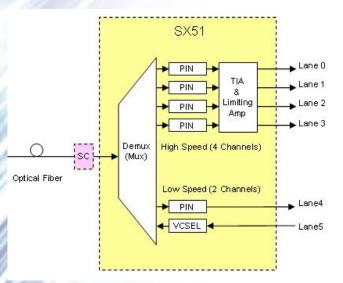

The P1RX6A-SX51x-O1 (RX-SX51) is an optical subassembly (OSA) with bi-direction comm and control link capabilities. The RX-SX51 can receive up to four video- or data-lanes (up to 3.5Gbps) and one low-speed lane, while simultaneously transmitting one low-speed signal, all on *a single* multimode fiber. With the TIA and Limiting Amplifier embedded in the OSA and a ZIF-terminated flex circuit, the RX-SX51 is a bi-directional ROSA also capable of transmitter a control signal thereby enabling increased flexibility in system design, extending to applications in DVI and HDMI<sup>™</sup> v1.4.

### **FEATURES**

- 5 receive lanes and 1 transmit lane

- HDMI<sup>™</sup> 1.4-capable

- Integrated TIA and Limiting Amp

- Low-stress, highly flexible ZIF connection

- Low power consumption

- High-speed CML outputs

### **APPLICATIONS**

- High-speed Optical Links

- DVI Optical Extenders

- DVI Switches

- HDMI<sup>TM</sup> Matrix Switches

- HDMI<sup>TM</sup> Optical Extenders

### **ORDERING INFORMATION**

| PART NUMBER      | DESCRIPTION                                                                                                   |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------|--|--|--|--|

| P1RX6A-SX51D-01  | 4-ch Receiver Optical Subassembly,<br>3.5 Gbps per channel plus 5 Mbps Bi-di channel                          |  |  |  |  |

| P1RX6A-SX51D-01C | 4-ch Receiver Optical Subassembly,<br>3.5 Gbps per channel plus 5 Mbps Bi-di chanr<br>with Clip               |  |  |  |  |

| P1RX6A-SX51D-01H | 4-ch Receiver Optical Subassembly,<br>3.5 Gbps per channel plus 5 Mbps Bi-di channel<br>with Heatsink & Clip  |  |  |  |  |

| P1RX6A-SX51V-01  | 4-ch Receiver Optical Subassembly,<br>1.65 Gbps per channel plus 5 Mbps Bi-di char                            |  |  |  |  |

| P1RX6A-SX51V-01C | 4-ch Receiver Optical Subassembly,<br>1.65 Gbps per channel plus 5 Mbps Bi-di channel<br>with Clip            |  |  |  |  |

| P1RX6A-SX51V-01H | 4-ch Receiver Optical Subassembly,<br>1.65 Gbps per channel plus 5 Mbps Bi-di channel<br>with Heatsink & Clip |  |  |  |  |

### **BLOCK DIAGRAM**

P1RX6A-SX51x-01 ROSA

### **ABSOLUTE MAXIMUM RATINGS**

| PARAMETER                                              | SYMBOL          | MIN  | MAX | UNITS |

|--------------------------------------------------------|-----------------|------|-----|-------|

| Storage Temperature <sup>1</sup>                       | T <sub>st</sub> | -40  | 85  | °C    |

| Supply Voltage                                         | V <sub>cc</sub> | -0.3 | 3.6 | V     |

| Operating Ceramic (substrate) Temperature <sup>2</sup> | Ta              | 0    | 70  | °C    |

| Operating Humidity <sup>3</sup>                        | RH              |      | 80  | %     |

Notes:

1. Stresses listed may be applied without causing damage. Functionality at or above the values listed is not implied. Exposure to these values for extended periods may affect reliability.

2. See outline drawing for measurement point. Inneos strongly recommends mounting with a heat sink.

3. Non condensing humidity.

### **OPTICAL CHARACTERISTICS – HIGH-SPEED LANES**

| PARAMETER                         | SYMBOL          | MIN    | ТҮР    | MAX | UNITS |

|-----------------------------------|-----------------|--------|--------|-----|-------|

| Wavelength – Lane 0               | λο              | 760    | 778    | 860 | nm    |

| Wavelength – Lane 1               | $\lambda_1$     | 760    | 800    | 860 | nm    |

| Wavelength – Lane 2               | λ2              | 760    | 825    | 860 | nm    |

| Wavelength – Lane 3               | $\lambda_3$     | 760    | 850    | 860 | nm    |

| Peak Optical Input Power per Lane | P <sub>in</sub> |        |        | 4.0 | dBm   |

| OMA Sensitivity <sup>1</sup>      |                 | -14.25 | -16.00 |     | dBm   |

### Notes:

1. Optical Modulation Amplitude. Based on an unstressed input signal.

### ELECTRICAL SPECIFICATIONS – HIGH-SPEED LANES

| PARAMETER                                               | SYMBOL                 | MIN   | ТҮР   | MAX          | UNITS      |

|---------------------------------------------------------|------------------------|-------|-------|--------------|------------|

| Data Rate per Lane <sup>1</sup><br>SX51V-01<br>SX51D-01 | DR                     |       |       | 1.65<br>3.50 | Gb/s       |

| Low Frequency Cutoff                                    | F <sub>CUTOFF</sub>    |       | 125   | 300          | kHz        |

| Total Jitter (RMS), per lane <sup>2</sup>               | T <sub>J1</sub>        |       | 10    |              | ps         |

| Differential Output Voltage <sup>3</sup>                | V <sub>Out-DIFF</sub>  | 400   | 600   | 2000         | $mV_{p-p}$ |

| Loss of Signal Assert Sensitivity                       | LOS <sub>SEN-ON</sub>  | -20   | -17   | -13          | dBm        |

| Loss of Signal De-Assert Sensitivity                    | LOS <sub>SEN-OFF</sub> | -19.5 | -15.5 | -11          | dBm        |

| Loss of Signal Output Low <sup>4</sup>                  | V <sub>LOSL</sub>      |       |       | 0.7          | V          |

| Loss of Signal Output High                              | V <sub>LOSH</sub>      | 2     |       |              | V          |

| Operating Supply Voltage                                | V <sub>CC</sub>        | 3.15  | 3.30  | 3.45         | V          |

| Operating Supply Current                                | Icc                    |       | 91    |              | mA         |

#### Notes:

1. Requires DC-balanced data pattern. Measured with input signals conforming to HDMI rev 1.3a, Section 4.2.4, Figure 4-18.

2. Based on a jitter-free source.

3. Differential CML compatible inputs.

4. This output is asserted high when a loss of signal is detected on all lanes.