## FG600-CL, A PXIE, OPEN FPGA, BASED CAMERALINK FRAME GRABBER

Home / Products / Systems / Imaging / FG600-CL, a

PXIe, open FPGA, Based CameraLink Frame Grabber

## Request pricing or more information

| Description     | Features and Applications | Additional Images | IP Cores/Drivers/BSP |

|-----------------|---------------------------|-------------------|----------------------|

| Ordering Inform | ation                     |                   |                      |

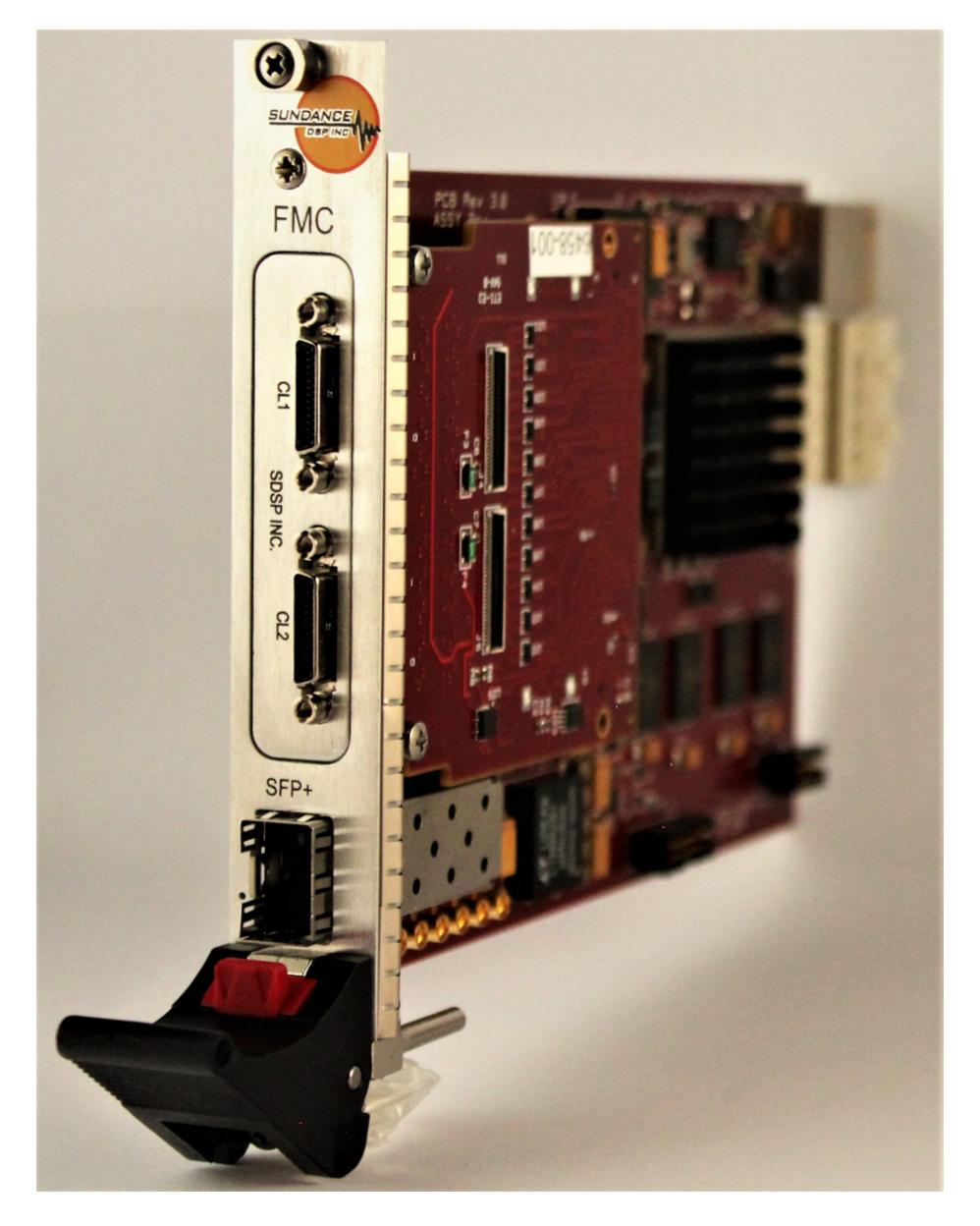

**FG600-CL** is a PXIe format, FPGA based imaging solution that supports BASE, MEDIUM, FULL and Extended FULL CameraLink compatible cameras. The hardware is fully compliant with the PXIe standard and can be used in a PXIe chassis as well as in an embedded fashion. The PXIe700 based card, used in this solution, can be found on SDSP web site for full details. The board offers 4 lanes of Gen2 PCIe for host communication. An FMC-CL Cameralink FMC card is attached to the base card for interfacing to the cameras.

| Interface        | FG600CL-PXIe | Number of Cameras +(option) |

|------------------|--------------|-----------------------------|

| Base CL          | $\checkmark$ | 2 (2)                       |

| Medium CL        | $\checkmark$ | 1 (1)                       |

| Full CL          | $\checkmark$ | 1 (1)                       |

| Extended Full CL | $\checkmark$ | 1 (1)                       |

| 1x SATA-3        | √            |                             |

| 2x SATA-3        | √ or SFP+    |                             |

The FG600-CL has a variety of I/O capabilities – 2 x SATA connectors for real-time storage of image frames (needs suitable IP core which is not included) and an SFP+ for transfer of images via Ethernet connection. The x2 SATA can also be used as general purpose I/O.

FG-600CL base board (PXIe700) comes with a Kintex7 XC7K410T in FFG900 package and includes:

- PXI control, trigger and clock

- 4 Lane PCIe Gen2 (Gen3 with softcore)

- SFP+ cage for 10Gb Ethernet or Fiber Optics

- JTAG

- White Rabbit support for nanosecond synchronization

• 2 banks of DDR3 memory, 1GB each, 32-bit wide and 128MB of FLASH

With an open FPGA the hardware is fully user- programmable to implement customized IP cores.

The package comprises PXIe700 FPGA card, FMC-CL Cameralink interface FMC, CameraLink capture and set up IP cores, PCIe driver, demo application, host API library, and a full user guide. Demo includes set up of camera, capture of image and buffered in FPGA for transfer to host over PCIe interface.

## **Related Products**

SMT580, PCIe to PXIe adapter card

FG-650CL, a

PCle, open

FPGA, Based

CameraLink

Frame Grabber

FG-550-CL, embedded, Xilinx Zynq FPGA-based, Cameralink solution

FMC-CL, Cameralink frame-grabber

About Us | Disclaimer | Sitemap | Terms & Conditions | License Agreement | Jobs

Copyright © 2020 - Sundance DSP Inc.

Email this page